W957D6HB

128Mb Async./Burst/Sync./A/D MUX

TABLE OF CONTENTS

1. GENERAL DESCRIPTION .......................................................................................................... 3

2. FEATURES.................................................................................................................................. 3

3. ORDERING INFORMATION ....................................................................................................... 3

4. PIN CONFIGURATION ................................................................................................................ 4

4.1 Ball Assignment ............................................................................................................................... 4

5. PIN DESCRIPTION ..................................................................................................................... 5

5.1 Signal Description ............................................................................................................................ 5

6. BLOCK DIAGRAM ...................................................................................................................... 6

7. INSTRUCTION SET .................................................................................................................... 7

7.1 Bus Operation .................................................................................................................................. 7

8. FUNCTIONAL DESCRIPTION .................................................................................................... 8

8.1 Power Up Initialization ..................................................................................................................... 8

8.1.1 Power-Up Initialization Timing ................................................................................................................... 8

8.2 Bus Operating Modes ...................................................................................................................... 8

8.2.1 Asynchronous Modes ................................................................................................................................ 8

8.2.1.1 READ Operation (ADV# LOW)......................................................................................................................... 9

8.2.1.2 WRITE Operation (ADV# LOW) ....................................................................................................................... 9

8.2.2 Burst Mode Operation.............................................................................................................................. 10

8.2.2.1 Burst Mode READ (4-word burst) ................................................................................................................... 10

8.2.2.2 Burst Mode WRITE (4-word burst) ................................................................................................................. 11

8.2.2.3 Refresh Collision During Variable-Latency READ Operation ......................................................................... 12

8.2.3 Mixed-Mode Operation ............................................................................................................................ 13

8.2.4 WAIT Operation ....................................................................................................................................... 13

8.2.4.1 Wired-OR WAIT Configuration ....................................................................................................................... 13

8.2.5 LB#/ UB# Operation................................................................................................................................. 14

8.3 Low Power Operation .................................................................................................................... 14

8.3.1 Standby Mode Operation ......................................................................................................................... 14

8.3.2 Temperature Compensated Refresh ....................................................................................................... 14

8.3.3 Partial-Array Refresh ............................................................................................................................... 14

8.3.4 Deep Power-Down Operation .................................................................................................................. 14

8.4 Registers ....................................................................................................................................... 15

8.4.1 Access Using CRE .................................................................................................................................. 15

8.4.1.1 Configuration Register WRITE Asynchronous Mode Followed by READ Operation ...................................... 15

8.4.1.2 Configuration Register WRITE Synchronous Mode Followed by READ Operation ........................................ 16

8.4.1.3 Configuration Register READ Asynchronous Mode Followed by READ ARRAY Operation ........................... 17

8.4.1.4 Configuration Register READ Synchronous Mode Followed by READ ARRAY Operation ............................ 18

8.4.2 Software Access ...................................................................................................................................... 19

8.4.2.1 Load Configuration Register ........................................................................................................................... 19

8.4.2.2 Read Configuration Register .......................................................................................................................... 20

8.4.3 Bus Configuration Register ...................................................................................................................... 20

8.4.3.1 Bus Configuration Register Definition ............................................................................................................ 21

8.4.3.2 Burst Length (BCR[2:0]) Default = Continuous Burst ..................................................................................... 22

8.4.3.3 Burst Wrap (BCR[3]) Default = No Wrap ........................................................................................................ 22

8.4.3.4 Sequence and Burst Length ........................................................................................................................... 23

8.4.3.5 Drive Strength (BCR[5:4]) Default = Outputs Use Half-Drive Strength ........................................................... 24

8.4.3.6 Table of Drive Strength ................................................................................................................................... 24

8.4.3.7 WAIT Configuration. (BCR[8]) ........................................................................................................................ 24

8.4.3.8 WAIT Polarity (BCR[10])................................................................................................................................. 24

8.4.3.9 WAIT Configuration During Burst Operation ................................................................................................... 25

8.4.3.10 Latency Counter (BCR[13:11]) Default = Three Clock Latency .................................................................... 25

8.4.3.11 Initial Access Latency (BCR[14]) Default = Variable ..................................................................................... 25

8.4.3.12 Allowed Latency Counter Settings in Variable Latency Mode ....................................................................... 25

Publication Release Date: Aug. 17, 2016

Revision: A01-005

-1-

�W957D6HB

8.4.3.13 Latency Counter (Variable Initial Latency, No Refresh Collision) .................................................................. 26

8.4.3.14 Allowed Latency Counter Settings in Fixed Latency Mode ........................................................................... 26

8.4.3.15 Latency Counter (Fixed Latency) ................................................................................................................. 27

8.4.3.16 Operating Mode (BCR[15]) ........................................................................................................................... 27

8.4.4 Refresh Configuration Register ............................................................................................................... 28

8.4.4.1 Refresh Configuration Register Mapping ....................................................................................................... 28

8.4.4.2 Partial Array Refresh (RCR[2:0]) Default = Full Array Refresh ....................................................................... 28

8.4.4.3 Address Patterns for PAR (RCR [4] = 1)......................................................................................................... 29

8.4.4.4 Deep Power-Down (RCR[4]) Default = DPD Disabled ................................................................................... 29

8.4.5 Device Identification Register .................................................................................................................. 29

8.4.5.1 Device Identification Register Mapping .......................................................................................................... 29

9. ELECTRICAL CHARACTERISTIC ........................................................................................... 30

9.1 Absolute Maximum DC, AC Ratings .............................................................................................. 30

9.2 Electrical Characteristics and Operating Conditions ....................................................................... 30

9.3 Deep Power-Down Specifications .................................................................................................. 31

9.4 Partial Array Self Refresh Standby Current .................................................................................... 31

9.5 Capacitance ................................................................................................................................... 31

9.6 AC Input-Output Reference Wave form.......................................................................................... 31

9.7 AC Output Load Circuit .................................................................................................................. 31

10. TIMING REQUIRMENTS ......................................................................................................... 32

10.1 Read, Write Timing Requirements ............................................................................................... 32

10.1.1 Asynchronous READ Cycle Timing Requirements ............................................................................... 32

10.1.2 Burst READ Cycle Timing Requirements .............................................................................................. 33

10.1.3 Asynchronous WRITE Cycle Timing Requirements .............................................................................. 34

10.1.4 Burst WRITE Cycle Timing Requirements ............................................................................................ 35

10.2 TIMING DIAGRAMS .................................................................................................................... 36

10.2.1 Initialization Period................................................................................................................................. 36

10.2.2 DPD Entry and Exit Timing Parameters ................................................................................................ 36

10.2.3 Initialization and DPD Timing Parameters ............................................................................................. 36

10.2.4 Asynchronous READ ............................................................................................................................. 37

10.2.5 Single Access Burst READ Operation - Variable Latency..................................................................... 38

10.2.6 Four Word Burst READ Operation-Variable Latency ............................................................................ 39

10.2.7 Single-Access Burst READ Operation-Fixed Latency ........................................................................... 40

10.2.8 Four Word Burst READ Operation-Fixed Latency ................................................................................. 41

10.2.9 Burst READ Terminate at End-of-Row (Wrap Off) ................................................................................ 42

10.2.10 Burst READ Row Boundary Crossing ................................................................................................. 43

10.2.11 Asynchronous WRITE ......................................................................................................................... 44

10.2.12 Burst WRITE Operation—Variable Latency Mode .............................................................................. 45

10.2.13 Burst WRITE Operation-Fixed Latency Mode ..................................................................................... 46

10.2.14 Burst WRITE Terminate at End of Row (Wrap Off) ............................................................................. 47

10.2.15 Burst WRITE Row Boundary Crossing ................................................................................................ 48

10.2.17 Asynchronous WRITE Followed by Burst READ ................................................................................ 50

10.2.18 Burst READ Followed by Asynchronous WRITE ................................................................................ 51

10.2.19 Asynchronous WRITE Followed by Asynchronous READ .................................................................. 52

11. PACKAGE DESCRIPTION ..................................................................................................... 53

11.1 Package Dimension ..................................................................................................................... 53

12. REVISION HISTORY ............................................................................................................... 54

Publication Release Date: Aug. 17, 2016

Revision: A01-005

-2-

�W957D6HB

1. GENERAL DESCRIPTION

Winbond x16 ADMUX products are high-speed, CMOS pseudo-static random access memory developed for lowpower, portable applications. The device has a DRAM core organized. These devices are a variation of the industrystandard Flash control interface, with a multiplexed address/data bus. The multiplexed address and data functionality

dramatically reduce the required signal count, and increase READ/WRITE bandwidth.

For seamless operation on a burst Flash bus, Winbond x16 ADMUX products incorporate a transparent self-refresh

mechanism. The hidden refresh requires no additional support from the system memory controller and has no

significant impact on device READ/WRITE performance.

Two user-accessible control registers define device operation. The bus configuration register (BCR) defines how the

Winbond x16 ADMUX device interacts with the system memory bus and is nearly identical to its counterpart on burst

mode Flash devices. The refresh configuration register (RCR) is used to control how refresh is performed on the

DRAM array. These registers are automatically loaded with default settings during power-up and can be updated

anytime during normal operation.

Special attention has been focused on standby current consumption during self refresh. Winbond x16 ADMUX

products include two mechanisms to minimize standby current. Partial-array refresh (PAR) enables the system to limit

refresh to only that part of the DRAM array that contains essential data. Temperature-compensated refresh (TCR)

uses an on-chip sensor to adjust the refresh rate to match the device temperature—the refresh rate decreases at

lower temperatures to minimize current consumption during standby. The system-configurable refresh mechanisms

are accessed through the RCR.

Winbond x16 ADMUX device is compliant with the industry-standard CellularRAM 1.5 x16 A/D MUX.

2. FEATURES

• Supports asynchronous, page, and burst operations

• Low-power features

• VCC, VCCQ Voltages:

On-chip temperature compensated refresh (TCR)

1.7V–1.95V VCC

Partial array refresh (PAR)

1.7V–1.95V VCCQ

Deep power-down (DPD) mode

• Random access time: 70ns

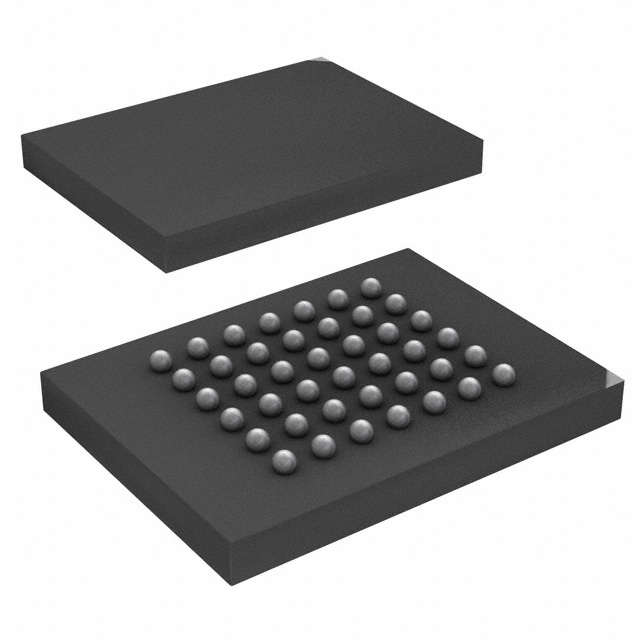

• Package: 54 Ball VFBGA

• Burst mode READ and WRITE access:

•16-bit multiplexed address/data bus

•Operating temperature range:

4, 8, 16, or 32 words, or continuous burst

-40°C ≤ TCASE ≤ 85°C

Burst wrap or sequential

Max clock rate: 133 MHz (tCLK = 7.5ns)

• Low power consumption:

Asynchronous READ: 20ns.

4. CE# must go HIGH before any clock edge following the last word of a defined-length burst.

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 46 -

�W957D6HB

10.2.14 Burst WRITE Terminate at End of Row (Wrap Off)

CLK

A[max:16]

VIH

VIL

VIL

ADV#

VIH

VIL

LB#/UB#

VIH

VIL

WE#

OE#

CE#

tCLK

VIH

VIH

VIL

VIH

VIL

VIH

Note 2

VIL

tSP

A/DQ[15:0]

tCSP

tHD

VIH

VIL

tHD

Valid

Input

Valid

Input

Valid

Input

END OF ROW

tHZ

tHZ

VOH

WAIT

VOL

HIGH-Z

tKOH

tKHTL

Don't Care

Undefined

Notes:

1. Non-default BCR settings for burst WRITE at end of row: fixed or variable latency, WAIT active LOW, WAIT asserted

during delay (shown as solid line).

2. For burst WRITEs, CE# must go HIGH before the second CLK after the WAIT period begins (before the second CLK

after WAIT asserts with BCR[8] = 0, or before the third CLK after WAIT asserts with BCR[8] = 1).

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 47 -

�W957D6HB

10.2.15 Burst WRITE Row Boundary Crossing

CLK

VIH

VIL

tCLK

A[max:16]

ADV#

VIH

VIL

VIH

VIL

VIH

LB#/UB#

WE#

VIL

VIH

VIL

VIH

OE#

VIL

CE#

VIH

VIL

tSP

A/DQ[15:0]

VIH

VIL

End of row

tHD

Valid

Input

Valid

Input

Valid

Input

Valid

Input

tKHTL

Valid

Input

tKHTL

VOH

WAIT

VOL

tKOH

tKOH

Note 2

Don't Care

Undefined

Notes:

1. Non-default BCR settings for burst WRITE at end of row: fixed or variable latency, WAIT active LOW, WAIT asserted

during delay (shown as solid line).

2. WAIT will be asserted LC cycles for variable latency or fixed latency.

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 48 -

�W957D6HB

10.2.16 Burst WRITE Followed by Burst READ

tCLK

CLK

A[max:16]

VIH

VIL

tSP tHD

tSP tHD

Valid

Address

Valid

Valid

Address

Address

VIH

VIL

tHD

ADV#

VIH

VIL

tSP

tSP tHD

tHD

tSP

VIH

LB#/UB#

VIL

tCSP

CE#

tHD tCBPH

VIH

Note 2

VIL

tCSP

tOHZ

VIH

OE#

tHD

VIL

WE#

VIH

tSP tHD

tSP

VIL

tSP

A/DQ[15:0]

IN/OUT

VIH

tSP tHD

tSP tHD

Valid

D0

D1

D2

D3

output

VIL

tHD

VOH

WAIT

Valid

Address

tKOH

tBOE

VOH

VOL

Valid

Output

Valid

Output

Valid

Output

Valid

Output

tACLK

HIGH-Z

HIGH-Z

VOL

Don't Care

Undefined

Notes:

1. Non-default BCR settings for burst WRITE followed by burst READ: fixed or variable latency, latency code 2 (3 clocks),

WAIT active LOW, WAIT asserted during delay.

2. A refresh opportunity must be provided every tCEM. A refresh opportunity is satisfied by either of the following two

conditions: a) clocked CE# HIGH, or b) CE# HIGH for longer than 15ns.

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 49 -

�W957D6HB

10.2.17 Asynchronous WRITE Followed by Burst READ

tCLK

CLK

VIH

VIL

tSP

A[max:16]

VIH

VIL

ADV#

VIH

VIL

LB#/UB#

VIH

VIL

tAVS

tAS

tVP

tAVH

tSP tHD

tAS

tSP

tBW

tCBPH

CE#

VIH

VIL

tHD

Valid

Address

Valid

Address

tHD

tCSP

tCW

Note 2

OE#

VIH

VIL

tWC

tSP tHD

tWP

WE#

VIH

VIL

tAS

A/DQ[15:0]

tOHZ

VIH

VIL

Valid

Address

tAVS

VOH

WAIT

VOL

tBOE

tSP tHD

Data

tAVH

tDW

Valid

Address

tDH

tKHTL

VOH

Valid

Output

VOL

tACLK

Valid

Output

Valid

Output

Valid

Output

tKOH

HIGH-Z

Don't Care

Undefined

Notes:

1. Non-default BCR settings for asynchronous WRITE, with ADV# LOW, followed by burst READ: fixed or variable latency,

latency code 2 (3 clocks), WAIT active LOW, WAIT asserted during delay.

2. When the device is transitioning between asynchronous and variable-latency burst operations, CE# must go HIGH. CE#

can stay LOW when the device is transitioning to fixed-latency burst READs. A refresh opportunity must be provided

every tCEM. A refresh opportunity is satisfied by either of the following two conditions: a) clocked CE# HIGH, or b) CE#

HIGH for longer than 15ns.

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 50 -

�W957D6HB

10.2.18 Burst READ Followed by Asynchronous WRITE

tCLK

CLK

VIH

VIL

A[max:16]

VIH

VIL

tSP

tHD

Valid

Address

Valid

Address

tAVS

tAVH

tAW

tAS

tSP

ADV#

tHD

tVS

VIH

tVP

VIL

tHD

tCSP

CE#

tAS

tCW

VIH

VIL

Note 2

tOHZ

tBOE

OE#

tCBPH

tHZ

VIH

VIL

tSP

WE#

VIH

VIL

LB#/UB#

VIH

VIL

tOLZ

tHD

tWP

tHD

tSP

tSP

A/DQ[15:0] VIH

VIL

tHD

VOH

Valid

Address

Valid

Output

VOL

tBW

tAS

tKOH

tACLK

tWPH

tAVS

VIH

VIL

tAVH

Valid

Address

tDW

tDH

Valid

Input

tKOH

VOH

WAIT

VOL

HIGH-Z

HIGH-Z

tKHTL

tKHTL

READ burst identified

(WE# = HIGH)

Don't Care

Undefined

Notes:

1. Non-default BCR settings for burst READ followed by asynchronous WRITE using ADV#: fixed or variable latency,

latency code 2 (3 clocks), WAIT active LOW, WAIT asserted during delay.

2. When the device is transitioning between asynchronous and variable-latency burst operations, CE# must go HIGH. CE#

can stay LOW when the device is transitioning from fixed-latency burst READs; asynchronous operation begins at the

falling edge of ADV#. A refresh opportunity must be provided every tCEM. A refresh opportunity is satisfied by either of

the following two conditions: a) clocked CE# HIGH, or b) CE# HIGH for longer than 15ns.

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 51 -

�W957D6HB

10.2.19 Asynchronous WRITE Followed by Asynchronous READ

A[max:16]

VIH

Valid

Address

Valid

Address

VIL

tAVS

tAS

tAVH

tVS

ADV#

VIL

tAA

tAADV

tAW

tWR

tVP

VIH

tAVH

tAVS

tVP

tAS

tBHZ

tCVS

LB#/UB#

CE#

VIH

tBW

tBA

VIL

tCVS

VIH

tCPH

tHZ

tCO

tCW

Note 1

VIL

tOLZ

OE#

tOHZ

tOE

VIH

VIL

tWP

WE#

VIH

VIL

tAS

VIH

A/DQ[15:0] VIL

Valid

Address

tAVS

Valid

Input

tAVH

tDW

Valid

Address

tDH

tAVS

VOH

Valid

Output

VOL

tAVH

tAA

tAW

tOEW

WAIT

VOH

tHZ

HIGH-Z

VOL

Don't Care

Undefined

Note:

1. When configured for synchronous mode (BCR[15] = 0), CE# must remain HIGH for at least 5ns (tCPH) to schedule the

appropriate refresh interval. Otherwise, tCPH is only required after CE#-controlled WRITEs.

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 52 -

�W957D6HB

11. PACKAGE DESCRIPTION

11.1 Package Dimension

VFBGA 54Ball (6x8 mm2, Ball pitch: 0.75mm, Ø =0.4mm)

6

5

3

4

E1

2

1

A

PIN A1 INDEX

eE

A1

// bbb

PIN A1 INDEX

E

A

eD

B

C

D1

D

D

E

F

G

H

J

Φb

Φaaa

Φddd

ccc

SEATING PLANE

M

M

BALL LAND

SYMBOL

A

A1

D

D1

E

E1

b

aaa

bbb

ccc

ddd

eee

e

DIMENSION (mm)

MIN.

NOM.

MAX.

----1.00

0.29

0.34

0.24

8.00

7.90

8.10

6.00 BSC.

6.00

5.90

6.10

3.75 BSC.

0.40

0.35

0.45

0.15

0.20

----0.10

0.15

0.08

0.75

1

BALL OPENING

Note:

1. Ball land: 0.45mm, Ball opening: 0.35mm,

PCB Ball land suggested ≤ 0.35mm

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 53 -

�W957D6HB

12. REVISION HISTORY

Version

Date

Page

Description

A01-001

Feb. 22, 2013

All

A01-002

Mar. 26, 2013

2

1~38

Update ordering information

Add DPD mode

A01-003

May 09, 2013

All, 2

Update part #

A01-004

Jun. 27, 2013

32

A01-005

All

8

34

52

Aug. 17, 2016

3, 19, 20, 25, 29, 36

31

43

48

Create new document

Remove note 6 in section 9.2

Refine format

Refine 8.1.1 power-up initialization timing diagram

Removing redundant tWHZ parameter

Correcting typo in 10.2.19 timing diagram (change tDS to tDW )

Correcting typos

Defined 9.4 Partial Array Self Refresh standby current values

Revise note2 of 10.2.10 Burst READ Row Boundary Crossing

Revise note2 of 10.2.15 Burst WRITE Row Boundary Crossing

Important Notice

Winbond products are not designed, intended, authorized or warranted for use as components in systems or

equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship

instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for

other applications intended to support or sustain life. Furthermore, Winbond products are not intended for

applications wherein failure of Winbond products could result or lead to a situation where in personal injury,

death or severe property or environmental damage could occur.

Winbond customers using or selling these products for use in such applications do so at their own risk and

agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

Publication Release Date: Aug. 17, 2016

Revision: A01-005

- 54 -

�